软件定义芯片,硬汉赛灵思放大招要“软”倒所有程序猿?

2019-10-11 11:08:07爱云资讯

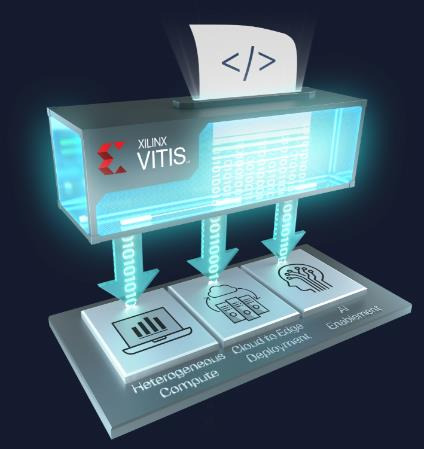

Vitis平台不限制使用专有开发环境,可以插入到通用的软件开发工具中,并利用丰富的优化过的开源库,使开发者能够专注于算法的开发。Vitis独立于Vivado™ 设计套件,后者仍然继续为希望使用硬件代码进行编程的用户提供支持。但是,Vitis也能够通过将硬件模块封装成软件可调用的函数,从而提高硬件开发者的工作效率。

10月9日发布会上,赛灵思大中华区销售副总裁唐晓蕾(Maria)从器件到平台转型战略和产业发展趋势介绍了Vitis“应运而生”的现实意义:

赛灵思大中华区销售副总裁唐晓蕾(Maria)

目前,大家碰到的一个问题是创新的速度远远超过整个芯片的设计速度。现代技术如机器学习之类的创新速度,已经远远超越了芯片设计的周期。这意味着,如果您要设计和制造针对GoogLeNet优化的ASIC或GPU,那么当收到工厂发回的芯片时,最先进的技术已经发生了变化。这些问题基本上需要通过可编程或者是自适应的技术来进行解决。因此,赛灵思提供了面向架构的灵活应变能力,可自由让客户可定制的,基于赛灵思架构的软硬件一体化统一平台——Vitis。

随后,赛灵思软件和人工智能高级经理罗霖,就Vitis的技术细节、功能、资源及发展路线向我们详细进行了介绍。

赛灵思软件和人工智能高级经理罗霖

VITIS堆栈

Vitis平台构建在基于堆栈的架构之上,该架构可以无缝插入到开源的标准开发系统与构建环境,而且最重要的是,它包含一套丰富的标准库。

Vitis堆栈

基础层是Vitis目标平台。该平台由电路板和预编程I/O构成。第二层称为Vitis核心开发套件,覆盖开源赛灵思运行时库,以管理不同域间的数据移动,包括子系统、即将发布的Versal ACAP™内的AI引擎和必要的外部主机。此外,该层也提供编译器、分析器和调试器等核心开发工具。虽然赛灵思提供的是世界一流的设计环境,但是这些工具设计的目的是能与业界标准的构建系统与开发环境无缝集成。

在第三层,8个Vitis库提供400余种优化的开源应用。这8个库分别是:Vitis基本线性代数子程序(BLAS)库、Vitis求解器库、Vitis安全库、Vitis视觉库、Vitis数据压缩库、Vitis计量金融库、Vitis数据库集和Vitis AI库。借助这些库,软件开发者可以使用标准的应用编程接口(API)来实现硬件加速。

VITIS AI和特定领域架构

Vitis平台的第4层,也是最具有变革意义的一层是Vitis AI。它集成了特定领域架构(DSA)。DSA提供了针对AI模型的硬件实现,开发者可以使用包括TensorFlow和Caffe等业界领先框架对其进行配置与编程。Vitis AI提供的工具链能在数分钟内完成优化、量化和编译操作,在赛灵思器件上高效地运行预先训练好的AI模型。此外,它也为从边缘到云端的部署提供了专用API,实现业界一流的推断性能与效率。赛灵思很快还将推出另一个DSA(Vitis Video),支持从FFmpeg直接进行编码并提供同样超级简单且功能极强大的端到端视频解决方案。由合作伙伴公司提供的DSA包括:与GATK集成用于基因分析的Illumina,与ElasticSearch集成用于大数据分析的BlackLynx,以及当前我们客户正在使用的专有DSA。

VITIS开发者网站

赛灵思还宣布推出了一个开发者网站,方便开发者获取示例、教程和文档,同时作为连接Vitis开发者社区的空间。它将由赛灵思和Vitis专家及爱好者共同管理,并将提供Vitis有关的最新更新、提示和技巧的宝贵信息。

最后,借用赛灵思总裁兼首席执行官(CEO) Victor Peng的话来做总结:“随着计算需求呈指数级增长,工程师与科学家常常受到固定芯片性能的局限。赛灵思打造了一个卓越的设计环境,使各学科领域的编程人员与工程师能够使用他们已熟知并掌握的工具和框架,共同开发与优化他们的软硬件。这意味着他们可以根据自己的应用调整硬件架构,而不需要新型芯片。”

由此可知,赛灵思推出统一软件平台,并不是不再专注于硬件芯片的研发。正相反,是希望通过打造卓越的设计环境,让更多的编程人员可以更好的去使用赛灵思芯片,更好的满足自身业务应用需求。

- 新点软件成功中标上海市综合监管运行管理系统建设项目

- 西安软件园与青软共建人才实训基地,公共平台同步上线促人才培养

- 新点软件荣登“2023智慧工地与智慧住建企业TOP50”引领行业智慧化新篇章

- 恭喜!达内教育&达内李欣老师荣获2023年度LF开源软件学园优秀合作伙伴&优秀讲师称号

- 新点软件出席华为中国合作伙伴大会2024,集“众志”奔赴“数智”

- 《2024年中国企业CRM软件国产替代趋势与应用研究报告》重磅首发!

- 充分释放数据价值 新点软件使能内蒙古通辽政务数据应用出实效

- 微创软件亮相CIF 2024第四届中国数智金融年会

- 钉钉与中国科学院软件所、达摩院合作,共同加速RISC-V应用落地

- 从冷冰冰到暖洋洋 新点软件助力内蒙古通辽政务数据“活起来”

- 润和软件携最新星闪产品亮相海思AWE2024展台

- 东软睿驰荣膺“中国汽车软件风云奖”两大奖项

- 金i奖揭晓 | 谷器数据创始人石龙当选“工业软件2023年度人物”

- 佛山市政数局联合新点软件开创新合作新思路

- 标贝科技亮相焉知汽车电子与软件生态合作科技节

- 佛山市政数局与新点软件签署联合创新开发协议