3纳米芯片面积比5纳米产品缩小35% 耗电量减少50%

2020-01-06 10:33:50AI云资讯516

三星电子副会长李在镕近日参观正在开发“全球第一个3纳米级半导体工艺”的韩国京畿道华城半导体工厂,并听取了关于3纳米工艺技术的报告,他还与三星电子半导体部门社长团讨论了新一代半导体战略。

据了解,三星电子计划利用极紫外光刻(EUV)工艺,提高在7纳米以下精细工程市场的份额。3纳米级半导体工艺计划首先应用到三星的晶圆代工(foundry)工程之中。三星计划明年下半年在全球最早实现3纳米级芯片的批量生产。

三星电子将在最新的3纳米工程中使用不同于其他工程的新一代工艺“GAA”。三星电子负责半导体产业的部门表示,基于GAA工艺的3纳米芯片面积可以比最近完成开发的5纳米产品面积缩小35%以上,耗电量减少50%,处理速度可提高30%左右。

相关文章

- 高拓讯达发布双天线 Wi-Fi 6 + 蓝牙三模芯片 ATBM6365

- OpenAI新模型发布,Meta/微美全息以AI芯片+模型布局加速行业创新进程

- 苹果MacBook Neo弃用博通网络芯片,转投联发科

- 硅谷首发,登陆AWE:图灵进化携算+存+电+连6款芯片来袭

- AWE 2026再携重磅阵容,MOVA全面披露芯片战略,擎画“主动时代”技术版图

- 阿里云金山算力中心加速投产,基于“真武”芯片建设超大规模算力中心

- 苹果 MacBook Air 展示国产游戏《异环》,M5 芯片运行开放世界画面

- Rambus推出HBM4E内存控制器:单芯片速度达4.1 TB/s,较HBM4提升60%

- 苹果发布M5 Pro和M5 Max芯片:18核处理器采用融合架构

- 苹果发布搭载M5芯片的MacBook Air及升级版MacBook Pro

- 高通推出骁龙可穿戴平台至尊版芯片,升级至3纳米制程

- 波罗密科技携手华科 智能芯片突破登《科学通报》获顶刊认证

- 中昊芯英“刹那®”TPU AI芯片Day0适配智谱GLM-5

- OpenAI首次采用Cerebras的AI芯片运行Codex模型,成功实现了每秒1000次事务处理量

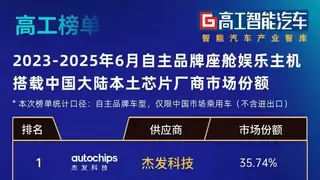

- 中国车市“芯”版图再扩容:本土企业稳居智能座舱芯片第一梯队

- 三星HBM4高带宽内存正式进入英伟达Vera Rubin人工智能芯片平台