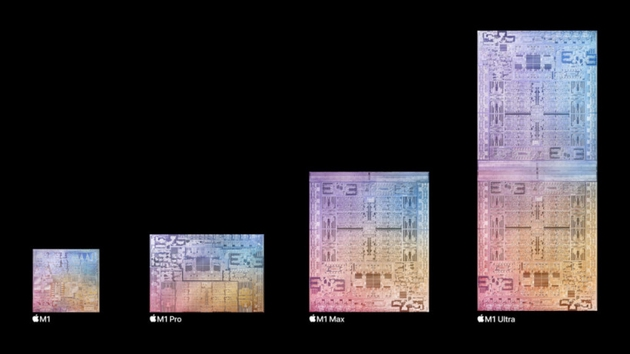

台积电确认苹果M1 Ultra采用InFO-LSI封装,将两片M1 Max连接到一起

2022-04-29 11:33:47AI云资讯1922

4月28日消息,在M1Ultra官方发布会上,苹果介绍其MacStudio中的M1Ultra时表示,这是最强大的定制AppleSilicon,它使用UltraFusion芯片对芯片互连技术,从而实现了2.5TB/s的带宽。

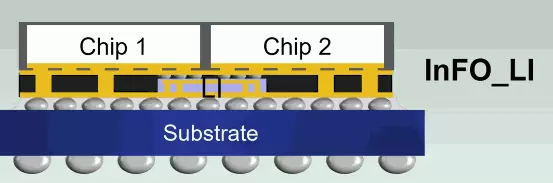

从介绍来看,这涉及到两个M1Max芯片协同工作的问题。台积电现已证实,苹果M1Ultra芯片其实并未采用传统的CoWoS-S2.5D封装生产,而是使用了本地的芯片互连(LSI)的集成InFO(IntegratedFan-out)芯片。

苹果最新的M1系列产品基于台积电5nm工艺技术,但之前有媒体称其通用采用了台积电CoWoS-S(chip-on-wafer-onsubstratewithsiliconinterposer)封装工艺。当然,台积电在使用其CoWoS封装平台为网络IC和超大AI芯片等多种芯片解决方案供应商提供服务方面拥有丰富经验,而且台积电还一直在使用先进工艺和InFO_PoP技术制造iPhone芯片。

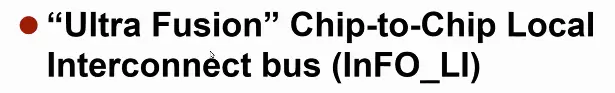

实际上有很多种可以将芯片组桥接进行相互通信,但台积电的InFO_LI可以降低成本。半导体封装工程专业人士TomWassick放出了一张台积电在3DIC和异构集成国际研讨会上呈现的PPT,阐明了其封装方法,显示苹果这次使用了InFO_LI技术。

总的来说,CoWoS-S是一种非常不错的方法,但要比InFO_LI更贵。除了这一点之外,Apple没必要选择CoWoS-S,毕竟M1Ultra只需要完成两个M1Max芯片的相互通信,而所有其他组件,包括统一的RAM、GPU和其他组件都是芯片中的一部分,因此,除非M1Ultra改用信新型多芯片设计和更快的内存(如HBM),否则InFO_LI对Apple来说就是更好的选择。

具体而言,InFO-LSI技术需要将一个本地LSI(siliconinterconnection)与一个重分布层RDL(redistributionlayer)相关联。与CoWoS-S相比,InFO-LSI的主要优势在于其较低的成本。

CoWos-S需要用到大量完全由硅制成的大型中介层,因此成本非常昂贵;但InFO_LI凑合着用了本地化的芯片互连技术,总的来说没什么太大影响。

值得一提的是,MarkGurman称,苹果新一代MacPro已经准备就绪,它将搭载一款更强的芯片,也就是M1Ultra的“继任者”。据称,这款产品的代号为J180,此前的信息暗示,这款产品将采用台积电的下一代4nm工艺量产,而不是目前的5nm工艺。

有传言称,新的苹果芯片将具有两个M1Ultra相结合(4个M1Max)。Gurman早些时候表示,这款工作站将采用定制的芯片,最多可支持40核CPU和128核GPU,性能值得期待,定价同样美丽。

相关文章

- 台积电或将取消苹果优先发货的待遇,因手机芯片已非首要营收来源

- 联发科即将推出天玑9600芯片,预计采用LPDDR6内存和台积电N2P制程工艺

- 台积电芯片需求火爆,客户为确保订单愿意支付高达100%的溢价

- 苹果或将与英伟达在台积电争夺相同的3D封装产能资源

- 台积电2纳米制程的流片数量已达到3纳米节点的1.5倍,苹果、高通和联发科的订单占据主要份额

- 良率优于预期,台积电决定加快建设1.4纳米晶圆厂

- 台积电 2 纳米 (N2) 技术已如期于 2025 年第四季开始量产

- 台积电在垄断性芯片市场的成功也带来焦虑:人工智能需求引发劳动力短缺与资本支出激增

- 因客户需求巨大,台积电预计将价格上调达10%

- 台积电计划将2纳米制程报价上调50%,高通联发科考虑转投三星2纳米产线

- 一骑绝尘!台积电以的份额主导全球代工市场

- M31与台积电发布N6e™ 平台超低功耗存储器编译器 加速AIoT创新

- 台积电2纳米制程工艺需求旺盛,将获高性能计算领域大规模采用

- 客户需求巨大!台积电亚利桑那工厂有望比原计划提前引入更先进的制程节点

- 台积电计划2029年前在美新建先进封装厂投产 自主供应链再进一步

- 台积电2纳米制程有望创下纪录:产能超越3纳米,科技巨头争相抢购引爆需求狂潮

人工智能企业

更多>>人工智能硬件

更多>>人工智能产业

更多>>人工智能技术

更多>>- 发布即适配| 天数智芯全力支持腾讯混元Hy3 preview 开源落地,共推国内大模型产业普惠

- Seedance 2.0面向企业公测,豆包大模型日均Token使用量突破120万亿

- 端到端OCR模型第一!百度千帆Qianfan-OCR正式发布

- 云知声Unisound U1-OCR大模型发布!首个工业级文档智能基础大模型,开启OCR 3.0时代

- 基石智算上线 MiniMax M2.5,超强编程与智能体工具调用能力

- 昇腾原生支持,科学多模态大模型Intern-S1-Pro正式发布并开源

- 百度千帆深度研究Agent登顶权威评测榜单DeepResearch Bench

- 在MoltBot/ClawdBot,火山方舟模型服务助力开发者畅享模型自由