面向下一代数据中心的全新CXL 3.1控制器IP

2024-02-23 09:22:35AI云资讯761

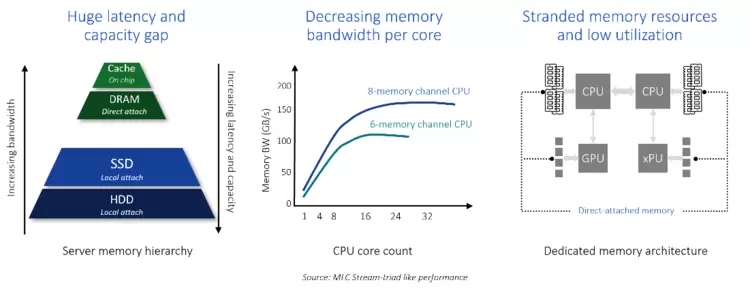

人工智能的快速发展正在引发数据中心的深入变革;计算密集型工作负载对CPU、加速器和存储之间的低延迟、高带宽连接提出了前所未有的高要求。Compute Express Link®(CXL®)互连技术为数据中心的性能和效率提升开辟了新的途径。

面对日益复杂的AI工作负载,数据中心各组件之间的高效通信变得至关重要。CXL通过提供低延迟、高带宽的连接来满足这一需求,从而提高整体内存和系统性能。

数据中心内存面临的挑战

CXL 3.1的数据传输速率高达64 GT/s并提供多层(网络连接)交换,可实现高度可扩展的内存池和共享。这些特色功能将成为下一代数据中心的关键,既能够减少高昂的内存成本和闲置的内存资源,又能够根据需要提供更高的内存带宽和容量。

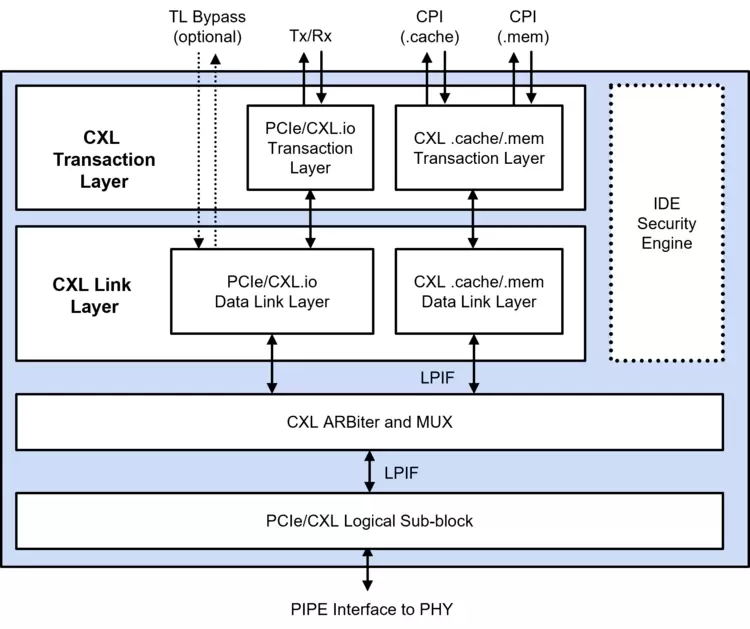

Rambus CXL 3.1控制器IP凭借灵活的设计,适用于ASIC和FPGA的实现。它采用适用于CXL.io协议的Rambus PCIe® 6.1控制器架构,并且增加了CXL特有的CXL.cache和CXL.mem协议。内置的零延迟完整性和数据加密(IDE)模块可提供最先进的安全性,防止针对CXL和PCIe链路的物理攻击。这款控制器既可以单独交付,也可以与客户选择的CXL 3.1/PCIe 6.1 PHY集成。

CXL 3.1 控制器模块图

Rambus半导体IP总经理Neeraj Paliwal表示:“生成式AI和其他高工作负载的性能需求需要由CXL支持的新架构解决方案。Rambus CXL 3.1数字控制器IP扩大了我们在这一关键领域的领先地位,为我们客户的尖端芯片设计提供了CXL最新演进标准中的吞吐量、可扩展性和安全。

CXL是数据中心的关键互连技术,可应对数据密集型工作负载所带来的诸多挑战。与Lou Ternullo一起参加我们即将召开的网络研讨会“挖掘CXL 3.1和PCIe 6.1在下一代数据中心中的潜力”,了解CXL和PCIe互连技术如何帮助设计人员优化数据中心内存基础设施解决方案。

相关文章

- 赋能电子、汽车、半导体、数据中心等产业,Fac Tec China电子工厂设施展邀您共赴6月2-4日上海世博展览馆

- 风液融合·微模块典范 | 科士达IDM荣膺数据中心创新产品大奖!

- 数据境内留存:ManageEngine 卓豪中国数据中心如何助力外企满足 PIPL 要求

- 科士达参编《预制化数据中心技术规范》 ,以全栈实力筑牢行业发展基石

- 中东数据中心遭“流弹”!白山云建议:跨云容灾要“物理隔离”

- 美光推出全球首款高容量256GB LPDRAM SOCAMM2,为数据中心基础架构树立新标杆

- 算力尽头是电力!易事特数据中心、UPS电源等赋能新疆哈密算力中心,打造算电协同标杆

- Anthropic表示将尽力避免数据中心推高用电成本

- 微软计划利用高温超导材料设计能效更高的数据中心

- 维谛技术(Vertiv)2026数据中心前瞻:一场正在发生的基础设施重构

- 马斯克称人工智能的发展速度将迫切需要建立轨道数据中心

- 马斯克宣称合并SpaceX与xAI,拟在太空建设数据中心

- SpaceX计划在轨道上部署100万个太阳能数据中心

- 马斯克的SpaceX与xAI或将合并,有助于推进太空数据中心发射计划

- Meta斥资640万美元开展宣传活动,争取公众对新建数据中心的支持

- OpenAI数据中心将自行承担能源成本并限制用水量

人工智能企业

更多>>人工智能硬件

更多>>- iQOO 15T正式发布:天玑9500 Monster版加持 全能体验无短板

- 从“+AI”到“AI+”:天禧AI 4.0加持,联想AI主机领衔L3级终端震撼登场

- 拾年匠音,声来不凡,致敬1000X系列十周年 索尼发布1000X十周年典藏版头戴降噪耳机

- 出游露营正当时 三星Galaxy手机全方位守护你的户外体验

- 拯救者Y900系列生产力大屏AI平板正式发布,学娱场景随心换,打造新一代旗舰终端

- 智慧陪伴 定格浪漫 三星Galaxy A57 5G让你的520心意满分

- 短途出行机器人QUORRA X5出海订单覆盖欧美,头部资本加持正奇未来布局全球

- 冠军之选,记录传奇:雷克沙x阿根廷国家队联名传奇定制系列三款新品齐发

人工智能产业

更多>>人工智能技术

更多>>- Twinkle x昇腾,率先实现Deepseek-V4系列模型高效训练

- 高德发布鸿蒙首个生成式 UI 开源框架 AGenUI,告别传统 UI 开发模式

- 发布即适配| 天数智芯全力支持腾讯混元Hy3 preview 开源落地,共推国内大模型产业普惠

- Seedance 2.0面向企业公测,豆包大模型日均Token使用量突破120万亿

- 端到端OCR模型第一!百度千帆Qianfan-OCR正式发布

- 云知声Unisound U1-OCR大模型发布!首个工业级文档智能基础大模型,开启OCR 3.0时代

- 基石智算上线 MiniMax M2.5,超强编程与智能体工具调用能力

- 昇腾原生支持,科学多模态大模型Intern-S1-Pro正式发布并开源